Investigadores de la Universidad de Bolonia, ETH Zurich y la Universidad de California en San Diego han publicado un artículo titulado «TOP: Hacia compañías petroleras homogéneas, abiertas y heterogéneas y predecibles».

un resumen:

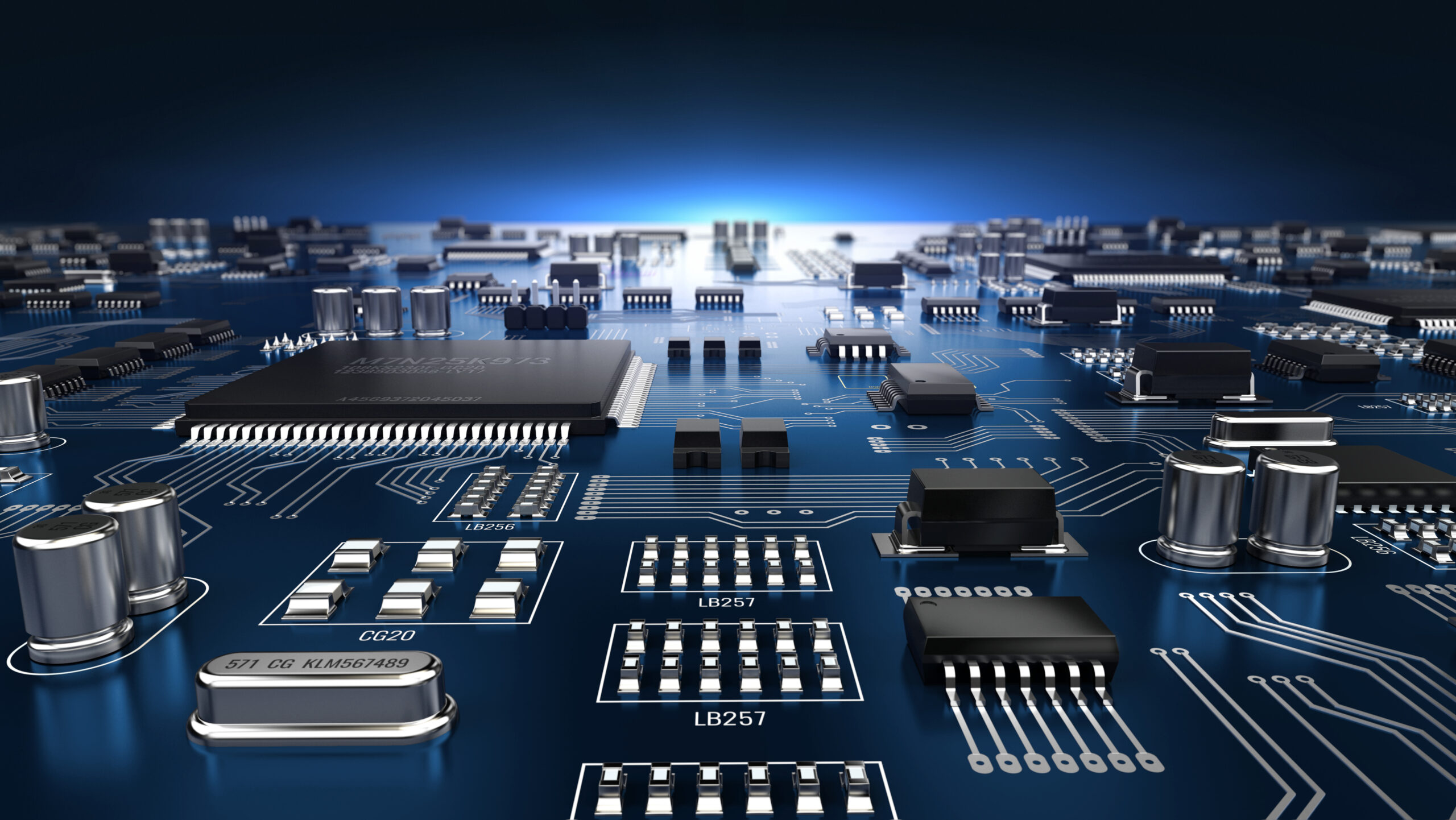

«Garantizar la previsibilidad en tiempo real en los sistemas modernos en chips (SoC) es una preocupación cada vez más importante para muchas áreas de aplicación, como la automoción, la robótica y la automatización industrial. Un enfoque eficaz implica modelar y desarrollar componentes de hardware, como interconexiones y recursos de memoria compartidos. para evaluar o hacer cumplir su comportamiento Lo inevitable: Desafortunadamente, estas IP a menudo son de código cerrado y estos estudios se limitan a módulos individuales que luego deben integrarse con IP de terceros en SoC más complejos, lo que dificulta la precisión y el alcance del modelado. y perjudica la previsibilidad general. Con la llegada de las arquitecturas de conjuntos de instrucciones de código abierto (RISC-V) y el hardware, se muestran importantes oportunidades para cambiar este status quo. Este estudio presenta una metodología innovadora para modelar y analizar el estado del código abierto. La última tecnología (SoA) para sistemas ciberfísicos de bajo consumo. Nuestro enfoque modela y analiza el conjunto completo de IP de código abierto dentro de los SoC. Luego proporciona un análisis exhaustivo de toda la arquitectura. Validamos esta metodología en un Muestra de una arquitectura RISC-V heterogénea de bajo consumo mediante simulación RTL e implementación de FPGA, lo que reduce el pesimismo en la determinación del tiempo de servicio de las transacciones que atraviesan la arquitectura entre un 28% y un 1%, que es mucho menor en comparación con ejecuciones SoA similares. «

Encontrar Ficha técnica aquí. Publicado en enero de 2024 (versión preimpresa). GitHub: https://github.com/pulp-platform/soc_model_rt_analogy

Valiente, Luca, Francesco Restuccia, Davide Rossi, Ryan Kastner y Luca Benigni. “ARRIBA: Hacia compañías petroleras abiertas, heterogéneas y predecibles”. Preimpresión de arXiv arXiv:2401.15639 (2024).

Lectura relacionada

Identificación de retrasos en el tiempo en SoC complejos

Los dispositivos de monitoreo en circuito se vuelven esenciales para comprender las causas de las fallas a lo largo del tiempo y en condiciones de operación realistas.

Verificación de microarquitectura RISC-V

La verificación del procesador es mucho más que simplemente asegurarse de que las instrucciones funcionen, pero la industria depende de una base de conocimientos limitada y pocas herramientas dedicadas.

Anatomía de una simulación de sistema.

Equilibrar los beneficios de un modelo con sus costos asociados es difícil, pero se vuelve aún más difícil cuando se combinan diferentes modelos.

«Defensor de la Web. Geek de la comida galardonado. Incapaz de escribir con guantes de boxeo puestos. Apasionado jugador».

More Stories

iOS 18: la nueva revisión de Apple revela una interesante función de privacidad de IA del iPhone

Google está trasladando Fitbit Pay a Google Wallet en la mayoría de los países

Las computadoras con tecnología de inteligencia artificial ofrecen grandes oportunidades para los MSP, dicen los proveedores de computadoras con tecnología de inteligencia artificial